���

�������������˲������ڽ��Ͷ�ADCǰ�õĿ�����˲�����Ҫ���ع�DAC����ͨ�����Ƶķ�ʽ���ù������Ͳ�ֵԭ�������磬������ƵCD�������������ù���������������CD�Ļ������ݸ�������Ϊ44.1 kSPS������CD������ʹ�ô�ͳ�Ķ�����DAC��������0�����벢�������У��Ӷ�����Ч����������ߵ������������ʵ�4����8����16����4����8����16��������ͨ��һ�����ֲ�ֵ�˲�����������������ݵ㡣�߹��������ʽ�����Ƶ���ƶ�������λ�ã��Ӷ�����ʹ�ý�Ϊ���ɱ����͡����ɴ��������˲��������⣬���ڴ��ڴ������棬�źŴ����ڵ�SNRҲ����ߡ���-����DAC�ܹ�ʹ�øߵö�Ĺ��������ʣ�����һԭ����չ�����£�������ִ�CD�����������ܻ�ӭ��

ͬ���Ĺ������Ͳ�ֵԭ��Ҳ������ͨ������ĸ���DAC���Ա㽵�Ͷ�����˲�����Ҫ�����ô����������SNR��

�ع�DAC�����Ƶ��

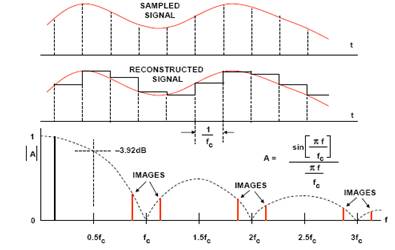

�ع�DAC��������Ա�ʾΪһϵ�о������壬����ȵ���ʱ�����ʵĵ�������ͼ1��ʾ��

ͼ1����ʾ�����sin (x)/x���������˲�DAC���

��ע�⣬���ο�˹��Ƶ��fc/2���ع��źŷ��Ƚ���3.92 dB�������Ҫ������ʹ��һ����sin(x)/x�˲�����������ЧӦ�������źŵľ�����Ϊ���������Ľ�����֣�����Ҳͨ��sin(x)/x����˥����

��������ֵDAC

������/��ֵDAC�Ļ���ԭ����ͼ2��ʾ��Nλ����������������fc���ա����ֲ�ֵ�˲����Ե��ڹ�����Ƶ��Kfc��ʱ�����ʹ������������������ݵ㡣�����Ƶ��Ӱ����ͼ2��ʾ�����ο�˹�ز���Ƶ����(A)����ģ�⿹�����˲�����Ҫ������൱�ߡ�ͨ���������Ͳ�ֵ�����Դ�ͶԸ��˲�����Ҫ����(B)��ʾ�����⣬���������ֲ��ڱ�ԭʼ�źŴ��������������ڣ���������Ҳ��������ߡ�ԭʼ�������ʼӱ�ʱ(K = 2)��SNR���3 dB��K = 4ʱ��SNR���6 dB������CD��������������һ�㣬һ���ܽ������˲����е��㷨��ȷ��Nλ���ϡ����CD�������еĶ���DAC���Ǧ�-���͡�

���ڹ�����/��ֵDACԭ����������������Ritchie��Candy��Ninke��1974���������ģ��ο�����1�����Լ�Mussman��Korte��1981�꣨�������ڣ������ר�����ο�����2����

ͼ2����������ֵDAC

����ʹ��һЩʵ�ʵ���ֵ��˵��������ԭ����������30 MSPS����������������һ����ͳDAC���μ�ͼ3A����DAC���Ƶ��Ϊ10 MHz����30 �C 10 = 20 MHzʱ�ľ���Ƶ�ʳɷֱ���ͨ��ģ�⿹����˲�������˥�����˲����Ĺ��ɴ�ʼ��10 MHz��ֹ��20 MHz��������뽫����Ƶ��˥��60 dB������10 MHz��20 MHz��һ����Ƶ�̣��Ĺ��ɴ��ڣ��˲��������10 MHz��ͨ��ת��Ƶ�ʱ�Ϊ60 dB�����˥�����˲���ÿ�������ṩ��Լ6 dB/��Ƶ�̵�˥������ˣ�Ϊ���ṩ�����˥����������Ҫ10�����㡣���ɴ�Խխ�����˲���Խ���ӡ�

ͼ3��fo = 10 MHzʱ��ģ���˲���Ҫ��(A) fc = 30 MSPS��(B) fc = 60 MSPS

�������ǽ�DAC����������ߵ�60 MSPS�����ڸ�ԭʼ���ݲ�����֮����롰0�������ڣ�����������Ϊ60 MSPS�������DZ���ȷ����ֵ���ݵ��ֵ����ͨ��������0��60 MSPS�������������ֲ�ֵ�˲���������ʵ�֣����˲��������������ݵ㡣2�� ������Ƶ���µ������˲�����Ӧ������ͼ3B��ʾ��ģ�⿹����˲���������������10 MHz��50 MHz����һ���������2fc �C fo = 60 �C 10 = 50 MHz�����ù������Դ���2����Ƶ�̣�˵��5��6�����˲������㹻��

AD9773/AD9775/AD9777(12-/14-/16-bit)ϵ�з���DAC (TxDAC®)��2����4����8����ѡ��������ֵ˫ͨ��DAC��ͼ4Ϊ���ͼ����Щ�����ܹ�������ߴ�160 MSPS��12/14/16λ���������ʣ�������������Ϊ400 MSPS���������Ƶ��Ϊ50 MHz�������������Ϊ160 MHz����������Ϊ2������Ƶ�ʳ�����320 MHz �C 50 MHz = 270 MHz�����ģ���˲����Ĺ��ɴ�Ϊ50 MHz��270 MHz�����û��2��������������Ƶ�ʳ�����160 MHz �C 50 MHz = 110 MHz���˲������ɴ�Ϊ50 MHz��110 MHz��

ͼ4����������ֵTxDAC®�ļ�ͼ

��Ӧע�⣬��������ֵDAC֧�ֽϵ͵�����ʱ��Ƶ�ʺ������������ʣ��������ϵͳ�ڲ��������Ŀ�����Ҫ�͵öࡣ

��-����DAC

��-����DAC�Ĺ���ԭ���릲-����ADC�dz����ƣ����ڦ�-����DAC�У��������ι������������ֵ�����ʵ�ֵģ�����������ģ���������

�릲-����ADC��ͬ����-����DAC���������ʽ���μ�ͼ5A��������һ������ֵ�˲�������һ�����ֵ�·���Ե����ʽ������ݣ��Ը����ʲ���0��Ȼ��Ӧ�������˲����㷨���Ը�����������ݣ���һ����-���͵������������ź��ǵ�ͨ�˲������������������Ǹ�ͨ�˲����������ɴ˲���������ת��Ϊ����λ������һ��1λDAC��ɣ���DAC������ڵ�ֵ��������ѹ֮���л���������ⲿģ���ͨ�˲���(LPF)���˲������ڹ�����Ƶ�ʺܸߣ���LPF�ĸ��Ӷ�Զ���ڴ�ͳ�ο�˹�ز���Ƶ���µ������

ͼ5����-����DAC

��-����DAC����ʹ�ö�λ�������ͼ5B��ʾ�ġ���λ���ܹ�����ԭ����֮ǰ���۵IJ�ֵDAC���ƣ����������˦�-�������ֵ�������

��ȥ������nλ�ڲ�DAC�ľ���Ҫ������Ȼֻ��nλ���������������λ��Nλ�����Զȣ�����λDAC������ơ�Ȼ����AD195xϵ����ƵDAC����ר�С����ݼ��š���������Ϊ�����ݶ�����š����������һ���⣬��������Ƶ����涼���ṩ��ɫ�����ܡ�

ͼ6��ʾΪAD1955 ��λ��-������ƵDAC�� AD1955ͬ��ʹ�����ݶ�����ż�����֧�ָ���DVD��Ƶ��ʽ�������зdz����Ĵ��ж˿ڡ�THD + N����ֵΪ110 dB��

ͼ6��AD1955��λ��-������ƵDAC

�ܽ�

���ִ����ݲ���ϵͳ�У���������������˲���ǿ�����Ĺ��ߡ������Ѿ�������ͬ���Ļ���ԭ����������ADC��Ҳ�������ع�DAC����Ҫ�ŵ��ǶԿ����/�������˲�����Ҫ����Խ��ͣ���һ���ŵ���SNR�����������ߡ�

��-����ADC��DAC�ܹ��ǹ�����ԭ�����ն���չ��ͬʱҲ�Ǵ��������Ƶ������Ƶ�źŴ�������ת����Ӧ�õ���ѡ�ܹ���

|