|

由差分信号驱动的差分电路不产生偶次谐波。在本文中,我们将讨论要减少二次谐波失真,有必要采用对称的 PCB 布局。即使看似与对称布局的轻微偏差也会将二次谐波的幅度提高几个分贝。

我们还将讨论实际上决定设计的偶次失真性能的是信号路径对称性而不是组件对称性。

衰减二次谐波的基本技术

通过差分信号驱动对称结构通常是抑制二次谐波的基本技术。让我们看看这种技术是如何工作的。

假设我们的非线性电路是无记忆的(即任何时刻的输出只依赖于同一时刻的输入)。我们可以使用以下等式来近似非线性输入输出特性:

vout(t)=α1vin(t)+α2vin2(t)+α3vin3(t)+α4vin4(t)+...vout(t)=α1vin(t)+α2vin2(t)+α3vin3(t)+α4vin4(t)+...

其中 vin(t)vin(t) 和 vout(t)vout(t) 分别是电路输入和输出信号。

在这个等式中,系数 α1α1 指定电路的线性增益,α2α2 表征二次谐波失真。为了分析二次谐波,我们可以忽略高阶失真系数 (α3,α4,?)(α3,α4,?) 得到以下简化方程:

vout(t)=α1vin(t)+α2vin2(t)vout(t)=α1vin(t)+α2vin2(t)

如果我们使用该电路的两个副本,一个用输入 vin(t)vin(t) 激励,另一个用 ?vin(t)?vin(t) 激励,我们将获得以下输出:

vout,+(t)=α1vin(t)+α2vin2(t)vout,+(t)=α1vin(t)+α2vin2(t)

vout,?(t)=α1(?vin(t))+α2(?vin(t))2=?α1vin(t)+α2vin2(t)vout,?(t)=α1(?vin(t))+α2(?vin(t))2=?α1vin(t)+α2vin2(t)

减去这两个输出,我们有:

vout,+(t)?vout,?(t)=2α1vin(t)vout,+(t)?vout,?(t)=2α1vin(t)

虽然各个电路会产生二次谐波,但差分输出可以理想地抑制失真分量。这是差分操作的一个非常重要的特性,并解释了为什么由差分信号驱动的差分电路不产生偶次谐波。

实际上,差分电路可能无法完全抑制偶次谐波。然而,与奇次谐波相比,差分结构的偶次谐波通常可以忽略不计。

示例:差分 ADC 接口可以降低二次谐波

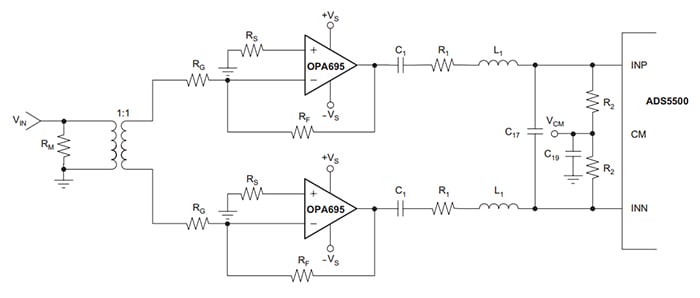

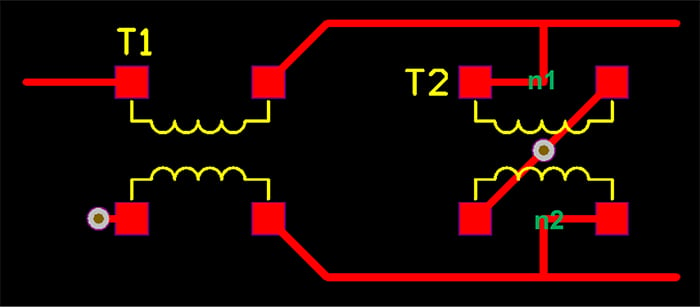

下图显示了一个示例应用,其中两个单端信号路径用于创建到 ADS5500 的差分接口,ADS5500是TI 的 14 位、125-MSPS 模数转换器。

图 1,图片由TI提供。

变压器将单端输入转换为差分信号。经过变压器后,两条信号路径完全相同。

值得一提的是,在实践中,变压器输出并不是理想的差分信号――两个输出之间可能存在相位和/或幅度不平衡。这些不平衡会增加二次谐波失真。可以看出,二次谐波幅度受相位不平衡的影响比受幅度不平衡的影响更严重。

布局对称性是二次谐波抑制的

除了在两个信号路径中使用相同的组件外,我们还需要采用对称的 PCB 布局来限度地消除二次谐波。非对称布局将阻止我们充分利用信号链中有源模拟模块(例如 ADC 和运算放大器)的线性度。

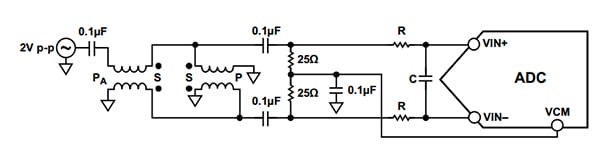

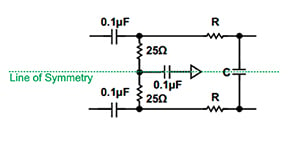

例如,考虑如下所示的 ADC 接口。

图 2. AD9266 ADC 的 ADC 接口。图片由Analog Devices提供。

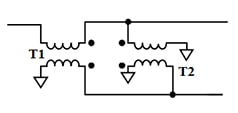

该 ADC 接口使用双巴伦配置(如下所示)将单端输入转换为差分信号。

图 3.用于单端到差分转换的双巴伦拓扑。

对于以 SNR 为关键参数的应用,这是一种常见的电路拓扑。与仅使用单个巴伦的结构相比,双巴伦配置可以减少差分输出之间的相位和幅度不平衡。AD9266 (Analog Devices 的 16 位 1.8 V ADC)数据表建议使用双平衡-不平衡变压器结构来实现大于约 10 MHz 的频率。

应仔细注意此级的布局,以尽量减少二次谐波失真。

双巴伦结构的示例布局

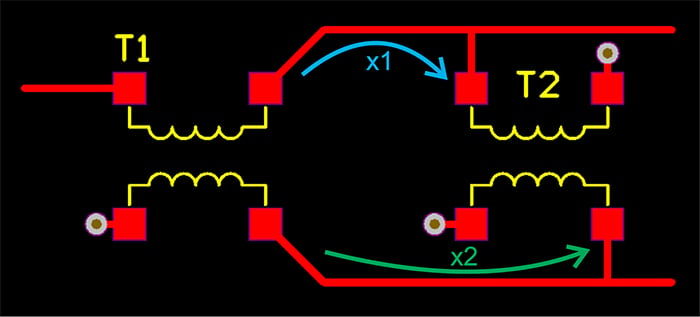

双巴伦结构的两种可能布局如图 4 和图 5 所示。

图 4 不是一个理想的布局,因为从 T1 到 T2 的走线对于上下信号路径是不同的(即,x1 和 x2 不相同)。

这种布局的另一个问题是 T2 的两个接地焊盘不对称。

图 4.双巴伦配置的非对称布局。

图 5 显示了该电路的另一种布局。在这种情况下,连接 T1 和 T2 的走线运行到中点(上路径为 n1,下路径为 n2),然后连接到 T2 的相应焊盘。这使得两条路径相同。此外,请注意对称走线用于 T2 的两个接地焊盘。

图 5.对称布局。

虽然这些调整可能看起来很微妙,但它们可以对设计的失真性能产生显着影响。与图 4 所示的布局相比,图 5 的对称布局可以将二次谐波幅度降低约 5dB。

元件对称性与信号路径对称性

要获得对称布局,我们有时可以从根据对称线放置组件开始。例如,上面图 2 中的电阻器和电容器可以如图 6 所示放置。

图 6

对于电阻器和电容器等两端元件,对称元件放置应导致对称布局。

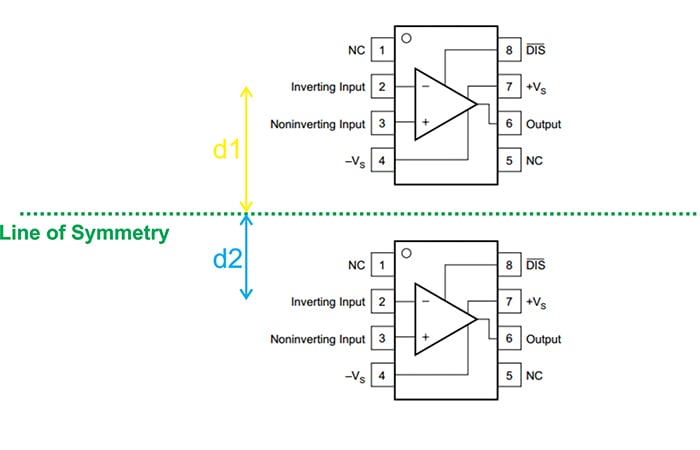

但是,非对称包不是这种情况。例如,考虑一个采用 SOIC-8 封装的运算放大器。如图 7 所示,相对于一条对称线放置其中两个封装不会创建对称布局。在此示例中,与下部运算放大器的反相输入相比,上部运算放大器的反相输入更远离对称线。换句话说,d1 > d2。

图 7

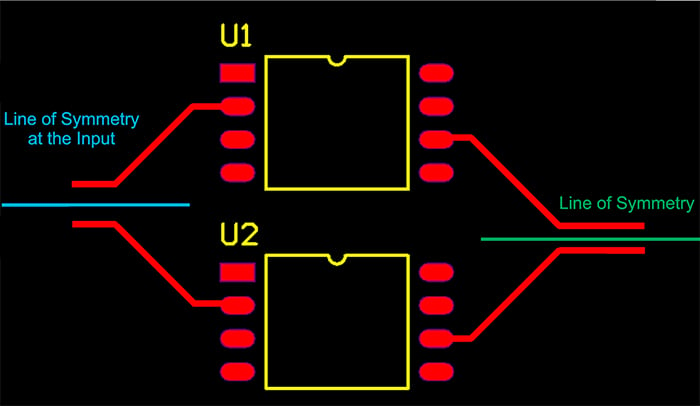

在这些情况下,我们必须考虑沿信号流路径的不同对称线,以保持信号对称性。

考虑下图:

图 8

下图显示了改变对称线如何让我们保持运行到运算放大器反相输入和运算放大器输出的走线的信号路径对称性。

|