|

DC/DC ���ؿ������� MOSFET ѡ����һ�����ӵĹ��̡��������� MOSFET �Ķ��ѹ�͵�����������ѡ���ʵ� MOSFET��Ҫ���� MOSFET ά���ڹ涨��Χ���ڣ������ڵ�դ����ɺ͵͵�ͨ����֮��ȡ��ƽ�⡣�ڶฺ�ص�Դϵͳ�У�����������ø��Ӹ��ӡ�

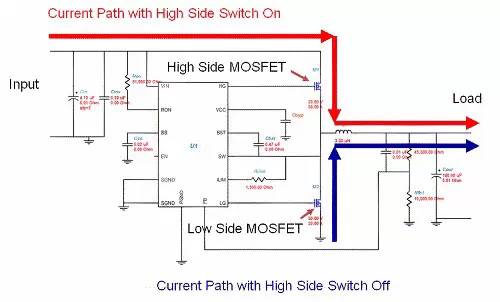

ͼ 1����ѹͬ��������ѹ��ԭ��ͼ

DC/DC ���ص�Դ�����Ч�ʶ��㷺Ӧ�����ִ��������ϵͳ�С����磬ͬʱӵ��һ���߲� FET�͵Ͳ� FET �Ľ�ѹͬ��������ѹ������ͼ 1 ��ʾ�������� FET ����ݿ��������õ�ռ�ձȽ��п��ز�����ּ�ڴﵽ����������ѹ����ѹ��ѹ����ռ�ձȷ���ʽ���£�

1) ռ�ձ� (�߲�FET,�Ϲ�) = Vout/(Vin*Ч��)

2) ռ�ձ� (�Ͳ�FET���¹�) = 1 �C DC (�߲�FET)

FET ���ܻἯ�ɵ��������һ����ͬһ��оƬ�У��Ӷ�ʵ��һ��Ϊ�Ľ�����������ǣ�Ϊ���ṩ�ߵ������������ﵽ����Ч�ʣ�FET ��Ҫʼ��Ϊ���������ⲿԪ�������������ʵ��ɢ����������Ϊ����FET���������ڿ�����������ӵ�е� FET ѡ������ԡ�����ȱ���� FET ѡ����̸��Ӹ��ӣ�ԭ����Ҫ���ǵ������кܶࡣ

һ�����������ǡ�Ϊʲô�������� 10A FET Ҳ�����ҵ� 10A ����أ����������� 10A ���������������������ơ�

ѡ�� FET ʱ��Ҫ���ǵ����ذ������ѹ�������¶ȡ�����Ƶ�ʡ�����������������ɢ�����������ؼ������ǣ�������Ĺ�����ɢ�Ȳ��㣬�� FET ���ܻ����������ǿ������÷�װ/ɢ����� ThetaJA �����������衢FET ���ĺͻ����¶ȹ���ij�� FET �Ľ��£����巽�����£�

3) Tj = ThetaJA * FET ���ģ�PdissFET�� + �����¶ȣ�Tambient��

��Ҫ����� FET �Ĺ��ġ����ֹ��Ŀ��Էֳ�������Ҫ���֣�AC �� DC ��ġ���Щ��Ŀ���ͨ�����з���ʽ����õ���

4) AC���: AC ���ģ�PswAC�� = ? * Vds * Ids * (trise + tfall)/Tsw

���У�Vds Ϊ�߲� FET �������ѹ��Ids Ϊ���ص�����trise �� tfall Ϊ FET ����ʱ��ͽ�ʱ�䣬��Tsw Ϊ�������Ŀ���ʱ�䣨1/����Ƶ�ʣ���

5) DC ���: PswDC = RdsOn * Iout * Iout * ռ�ձ�

���У�RdsOn Ϊ FET �ĵ�ͨ���裬�� Iout Ϊ��ѹ���˵ĸ��ص�����

��������γɵ�ԭ��������������ݡ�����ģ��Լ��Ͳ� FET ����ʱ���ڼ䵼����������������ģ����ڱ��������ǽ���Ҫ���� AC �� DC ��ġ�

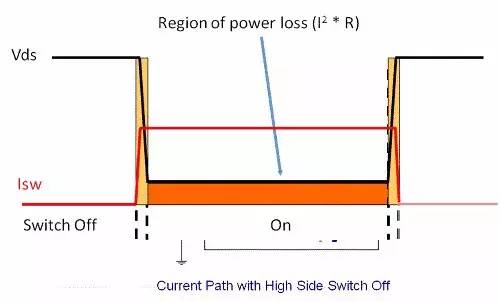

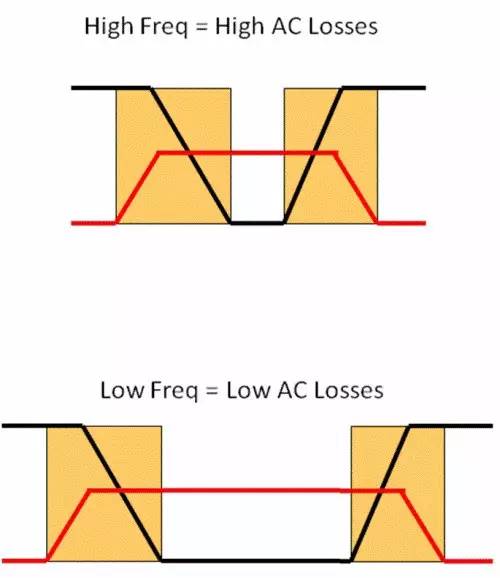

���ص�ѹ�͵�����Ϊ����ʱ��AC ������ij����ڿ��ص�ͨ�ض�֮��Ĺ����ڼ䡣ͼ 2 �и���������ʾ��������������ݷ���ʽ 4��������������ĵ�һ�ַ��������̿��ص���ʱ��ͽ�ʱ�䡣ͨ��ѡ��һ������դ����ɵ� FET�����Դﵽ���Ŀ�ꡣ��һ�������ǿ���Ƶ�ʡ�����Ƶ��Խ�ߣ�ͼ 3 ��ʾ�����������������ѵĿ���ʱ��ٷֱȾ�Խ����ˣ�����Ƶ�ʾ���ζ�Ÿ����AC������ġ����ԣ����� AC ��ĵ���һ�ַ������ǽ��Ϳ���Ƶ�ʣ�����Ҫ�������ͨ��Ҳ������ĵ����ȷ����ֵ���ص����������淶��

ͼ 2��AC ���ͼ

ͼ 3������Ƶ�ʶ� AC ��ĵ�Ӱ��

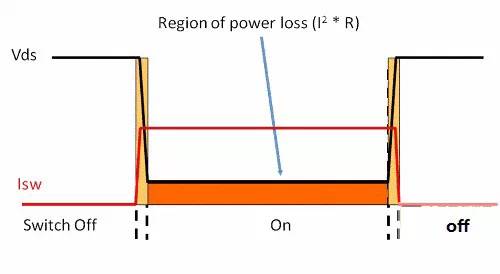

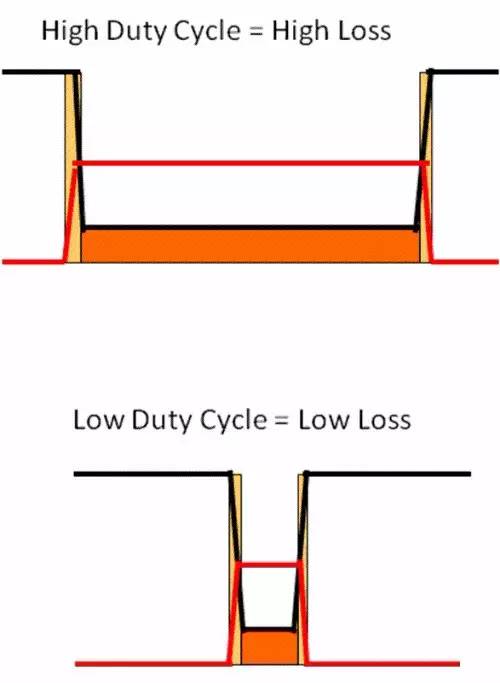

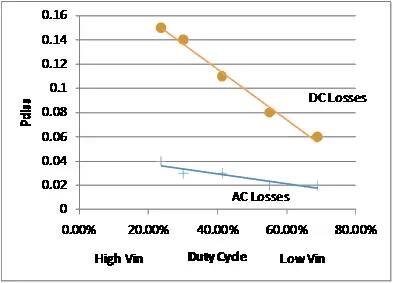

���ش��ڵ�ͨ״̬�³��� DC ��ģ���ԭ���� FET �ĵ�ͨ���衣����һ��ʮ�ּ� I2R ����γɻ��ƣ���ͼ 4 ��ʾ�����ǣ���ͨ������� FET ���¶��仯�����ʹ������������Ӹ��ӡ����ԣ�ʹ�÷���ʽ 3����4���� 5��ȷ���㵼ͨ����ʱ���ͱ���ʹ�õ�����������Ҫ���ǵ� FET ������������ DC ��ļ�һ�ַ�����ѡ��һ���͵�ͨ����� FET�����⣬DC ��Ĵ�СͬFET �İٷֱȵ�ͨʱ�����������ϵ����Ϊ�߲� FET������ռ�ձȼ��� 1 ��ȥ�Ͳ� FET ռ�ձȣ���ǰ��������ͼ 5 ���ǿ���֪���������ĵ�ͨʱ�����ζ�Ÿ����DC ������ģ���ˣ�����ͨ����С��ͨʱ��/FET ռ�ձ������� DC ��ġ����磬���ʹ����һ���м� DC ��ѹ�죬���ҿ����������ѹ������£������Ա�����Ϳ�����ռ�ձȡ�

ͼ 4��DC ���ͼ

ͼ 5��ռ�ձȶ� DC ��ĵ�Ӱ��

����ѡ��һ����դ����ɺ͵͵�ͨ����� FET ��һ�ּĽ��������������Ҫ�������ֲ���֮����һЩ���к�ƽ�⡣��դ�����ͨ����ζ�Ÿ�С��դ�����/���ٵIJ�������ܣ��Լ��ɴ˴����ĸߵ�ͨ���衣��һ���棬ʹ�ø���/���ಢ�������һ��ᵼ�µ͵�ͨ���裬�Ӷ����������դ����ɡ�����ζ�ţ�FET ѡ�����ƽ�����������ͻ�Ĺ淶�����⣬�����뿼�dzɱ����ء�

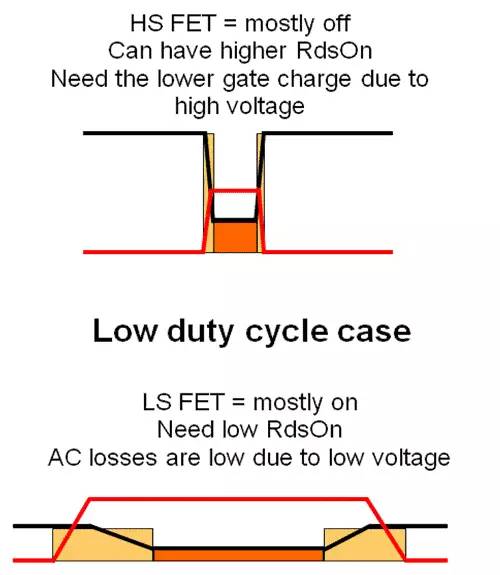

��ռ�ձ������ζ�Ÿ������ѹ������Щ��ƶ��ԣ��߲� FET ���ʱ���Ϊ�ضϣ���� DC ��Ľϵ͡����ǣ��� FET ��ѹ������ AC ��ģ����Կ���ѡ���դ����ɵ� FET����ʹ��ͨ����ϸߡ��Ͳ� FET �����ʱ���Ϊ��ͨ״̬������ AC ���ȴ��������Ϊ����ͨ/�ض��ڼ�Ͳ� FET �ĵ�ѹ�� FET ������ܶ��dz��ص͡���ˣ���Ҫѡ��һ���͵�ͨ����� FET������դ����ɿ��Ժܸߡ�ͼ 7 ��ʾ�����������

ͼ 7����ռ�ձ���Ƶĸ߲�͵Ͳ� FET ����

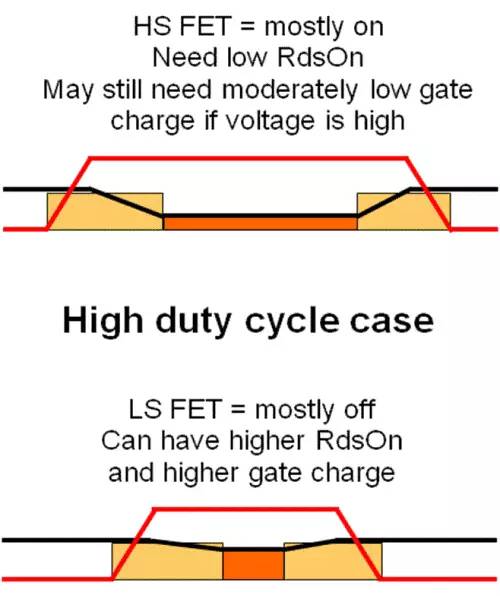

������ǽ��������ѹ�������ǿ��Եõ�һ����ռ�ձ���ƣ���߲� FET �����ʱ���Ϊ��ͨ״̬����ͼ 8 ��ʾ����������£�DC ��Ľϸߣ�Ҫ��͵�ͨ���衣���ݲ�ͬ�������ѹ��AC ��Ŀ��ܲ�����Ͳ� FET ʱ������Ҫ��������û�еͲ� FET �����͡���ˣ���ȻҪ���ʵ��ĵ�դ����ɡ���Ҫ���ڵ͵�ͨ����͵�դ�����֮��������Э���͵Ͳ� FET ���ԣ���ͨʱ��̣��� AC ��Ľϵͣ�������ǿ����ռ۸����������ǵ�ͨ�����դ�����ԭ��ѡ����ȷ�� FET��

ͼ 8����ռ�ձ���Ƶĸ߲�͵Ͳ� FET ����

����һ�����ص� (POL) ��ѹ��ʱ���ǿ��Թ涨ij���м��ѹ��Ķ�����ѹ����ô���������ʲô�أ��Ǹ������ѹ/��ռ�ձȣ����ǵ������ѹ/��ռ�ձ��أ�ʹ�ò�ͬ�����ѹ��ռ�ձȽ��е��ƣ�ͬʱ�鿴 FET���������

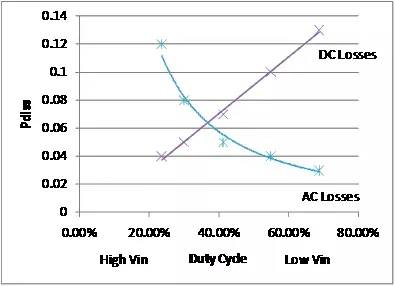

ͼ 9 �У��߲� FET ��Ӧ����ͼ������ռ�ձȴ� 25% ���� 40% ʱ AC ������Խ��ͣ���DC ���ȴ�������ӡ���ˣ�35% ���ҵ�ռ�ձȣ�ӦΪѡ����ݺ͵�ͨ����ƽ��FET������ֵ�����Ͻ��������ѹ�����ռ�ձȣ����Եõ���AC ��ĺ͵� DC ��ģ��ʹ˶��ԣ����ǿ���ʹ��һ���͵�ͨ����� FET��������ѡ���դ����ɡ���Ͳ� FET ͼ 10 ��ʾ��������ռ�ձ��ɵ�����ʱ DC ������Խ��ͣ��Ͳ� FET ��ͨʱ����̣����߿�����ռ�ձ�ʱ��ġ�������·���AC ��Ķ��ܵͣ�����κ�����¶�Ӧѡ��ʹ�õ͵�ͨ����� FET��

ͼ 9���߲�FET �����ռ�ձȵĹ�ϵ

ͼ 10���Ͳ� FET ����������ռ�ձȵĹ�ϵ����ע�⣺�Ͳ� FET ռ�ձ�Ϊ 1-������ռ�ձȣ���˵Ͳ� FET ��ͨʱ���������ռ�ձ����Ӷ�����

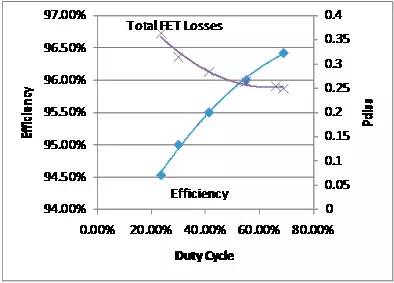

ͼ 11 ��ʾ�����ǽ��߲�͵Ͳ������ϵ�һ��ʱ��Ч�ʵı仯��������ǿ��Կ�������������£���ռ�ձ�ʱ��� FET ��ģ�����Ч�ʡ�Ч�ʴ� 94.5% ������ 96.5%�����ҵ��ǣ�Ϊ�˻�õ������ѹ�����DZ��뽵���м��ѹ���Դ�ĵ�ѹ��ʹ��ռ�ձ����ӣ�ԭ������ͨ��һ���̶������Դ���硣��ˣ��������ܻ������ POL ��õIJ��ֻ���ȫ�����档��һ�ַ����Dz�ʹ���м�죬����ֱ�Ӵ������Դ�� POL ��ѹ����Ŀ���ǽ�����ѹ��������ʱ��ռ�ձȽϵͣ����DZ���С�ĵ�ѡ�� FET��

ͼ 11���������Ч�ʺ�ռ�ձȵĹ�ϵ

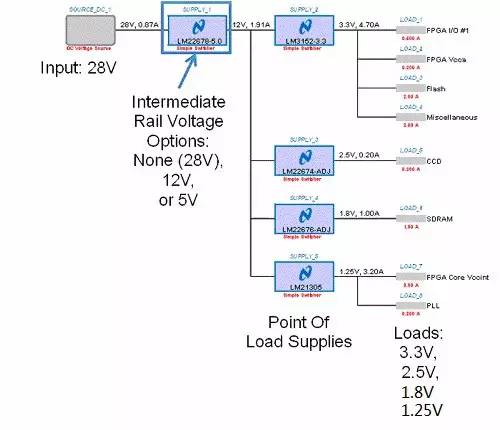

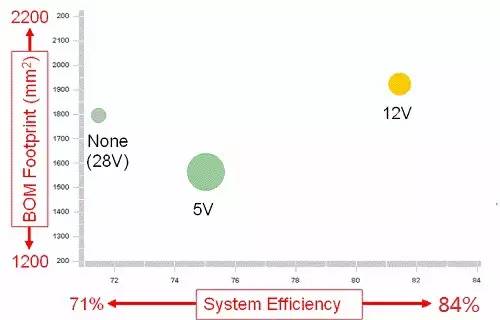

���ж�������ѹ�͵���Ҫ��ĵ�Դϵͳ�У��������Ӹ��ӡ��ԱȲ�ͬ POL ��ѹ��ռ�ձȵ�Ч�ʡ��ɱ��������ͼ 12 ��ʾ��һ��ϵͳ���������ѹΪ 28V������ 8 �����أ�4 ����ͬ��ѹ����ΧΪ 3.3V �� 1.25V������ 3 �ֶԱȷ�����1�����м�죬ֱ��ͨ�������Դ�ṩ 28V ��ѹ����ʵ�� POL ��ѹ���ĵ�ռ�ձȣ�2��ʹ�� 12V �м�죬POL��ѹ���е�ռ�ձȣ�3��ʹ�� 5V �м�죬�� POL ��ѹ��ռ�ձȡ�ͼ 13 �ͱ� 1 ��ʾ�˶ԱȽ������������£����м���Դ�Ĺ���ʵ���˳ɱ���12V�м���ѹ�Ĺ��ܻ����Ч�ʣ��� 5V �м���ѹ������ʵ�����������ˣ����ǿ��Կ������������ִ���ϵͳ���ԣ���POL��Դ�������������������Щ������û�����Ե�����������Ϊ��ʹ�ö����ѹ��ʱ�����м����ѹ���������⣬ÿ����ѹ�������䲻ͬ�ĸ��ص����͵�ѹҪ����Щ������ܻ����ͻ���о���������ķ�����ʹ���� WEBENCH ��Դ���ʦ�ȹ��ߣ��Բ�ͬ��ѡ���������

ͼ 12���������롢�м�졢���ص� (POL) ��Դ���صĵ�Դϵͳ���м���ѹ�IJ�ͬѡ��Ϊ 28V��ֱ��ʹ�������Դ����12V �� 5V����������ͬ�� POL ��ѹ��ռ�ձȡ�

ͼ 13 ��Դ�������ͼ��������м���ѹ�Ե�ԴϵͳЧ�ʡ�����ͳɱ���Ӱ�졣Բֱ��Ϊ BOM�������嵥���۸�

|

���ѹ

|

��

|

BOM ��� (mm2)

|

BOM �ɱ�

|

|

28V ����

|

71.5%

|

1795

|

$15.14

|

|

12V

|

81.4%

|

1923

|

$16.35

|

|

5V

|

75.0%

|

1564

|

$18.52

|

�� 1���м���ѹ�Ե�ԴϵͳЧ�ʡ�����ͳɱ���Ӱ�졣

|