|

尽管过去十年人们担心摩尔定律终会走到尽头,但微电子行业通过持续的创新和创造力,继续适应新的物理约束和产品要求。大部分创意能量都投入到了模拟、射频和混合信号模块作为嵌入式 IP 的开发中。

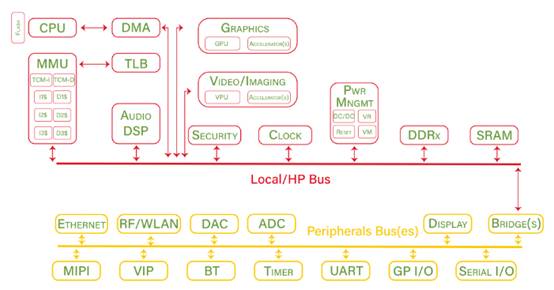

图 1该框图突出显示了多媒体 SoC 设计。P2F Semi

现在可用的模拟/射频/混合信号 IP 的选择既广泛又深入。人们可以在以下主要类别中找到大量 7 nm(有时甚至是 5 nm)的硬件模块:

PLL 和 DLL:提供多种速度、抖动和功率规格

DAC 和 ADC:分辨率为 8 位至 24 位,速率高达 300 MSPS

PHY 和 SerDes:针对广泛的市场选择,例如无线(Wi-Fi 和 5G)、网络(LAN、WAN 和存储)、计算(USB、PCIe、MIPI)和内存(DDR,包括 G 和 LP 变体,以及 HBM 和许多其他)

可以组装更小的组件来创建个性化模拟前端 (AFE)、电源管理功能和射频模块

该行业不断取得工艺技术进步,以支持对更高门数、更低功耗、更高性能和更多功能的永无止境的需求。其中包括三阱隔离、绝缘体上硅、P+ 保护环、FinFET 和沟槽隔离。其中许多功能促进了我们今天看到的模拟、射频和混合信号 IP 的激增。这些基板的添加还减少了设计人员在超深亚微米领域一直面临的一些复杂问题的严重程度,例如隐藏在转换速率中的模拟噪声源、阻抗匹配和端接复杂性以及支持巨大带宽的电路。

然而,面对 16 nm 及以下 SoC 设计中与模拟电路并排放置的大量门数,即使是新颖的工艺增强也显得不足。事实上,与模拟/射频宏非常接近的大型高性能数字模块带来的信号和电源完整性挑战正在从芯片扩展到封装和 PCB,而这两者都在努力跟上硅技术进步的步伐。SoC 设计人员越来越发现自己被迫将工作范围扩大到其他两个领域,以确保他们的芯片设计能够按预期运行。

这个由多部分组成的文章系列探讨了嵌入式模拟和 RF IP 核如何对芯片、封装和 PCB 功能产生负面影响,其影响是多种多样的。我们还将讨论如何在所有三个层面上防范这些问题,以及这些解决方案如何相辅相成。

硅实践

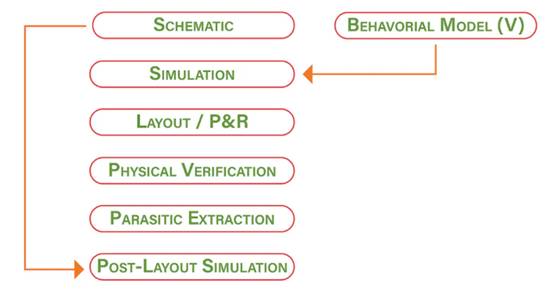

在过去的二十年里,为模拟和数字电路设计创建统一的工具和方法流程的尝试迄今为止已被证明是徒劳的。然而,人们对模拟流程的基本轮廓达成了普遍共识,如图2所示。

图 2显示基本模拟设计流程的视图。P2F Semi

尽管流程看起来相当简单,但细节决定成败。

模拟电路对电路的布局和布线方式非常敏感。设计规则(走线和通孔间距、差分信号和额外接地引脚)有助于避免或至少减少导致 EMI 问题的基板耦合和邻近效应。这就是为什么设计规则检查 (DRC) 是布局后物理验证工作的一部分。布局与原理图 (LVS) 检查也是验证预期连接性的同一步骤的一部分。

寄生参数提取直接影响潜在耦合源的识别,寄生参数的反向注释通常会导致原理图和布局的变化。不幸的是,这将影响时序、动态范围、负载、增益和功率,并产生一组全新的寄生效应。因此,返回设计流程开始的迭代循环是一种悲剧性的必然,这就是为什么模拟设计被认为更像是一门艺术而不是一门科学。

模拟块的集成

因此,将终的模拟模块集成到整个 ASIC/SoC 设计中会带来一系列全新的问题。对于数字和模拟电路模块,芯片布局规划将受到每个模块的位置、引脚布局、I/O 位置、关键路径、电源和信号分布以及芯片尺寸及其纵横比的限制。模拟 IP 对这些问题中的大多数都特别敏感,而模拟模块也是硬 MAC 的事实使上述所有问题变得复杂。

一旦放置了芯片的模块,布线实践包括首先实现所有关键路径,无论是模拟还是数字。然而,当涉及非关键路径时,模拟信号应优先。此外,无论给定的模拟信号是否至关重要,所有模拟布线都需要在匹配寄生效应、化耦合效应和避免过多的 IR 压降方面进行特殊考虑。它是通过采用模拟信号路由的各种屏蔽技术、保持走线短、通过直接的路由、差分信号等路由返回信号路径来实现的。

除了这些在片上集成模拟内容的广泛方法之外,不同类别的模拟电路也可能需要特别注意。DAC 和 ADC 就是一个完美的例子。

使用 DAC 或 ADC 时,除了其分辨率和采样率之外,还有一些设计注意事项,即其规格信噪比 (SNR)、有效位数 (ENOB) 额定值和功耗。遵循奈奎斯特采样定理(该定理指出,模拟信号的充分数字再现需要以超过模拟 F max的 2 倍的采样率进行采样)本身就会给高性能应用带来带宽、功耗和位同步挑战。

从采样的角度来看,无线尤其成问题,而音频通常对分辨率要求。这就是 ENOB 等参数具有特殊相关性的地方。无论给定 DAC 或 ADC 的宣传分辨率是多少,将此类块推过其 ENOB 都会降低其 SNR 性能,从而对该块的真正有用性产生潜在的重大影响。

重要的是,模拟模块设计和集成到 SoC 或 ASIC 环境中根本不像芯片的数字部分那样“干净”和可预测的工程工作。经验、灵活性和适应性是成功的决定因素。

|