|

要点汇总

1 PVDD去耦电容

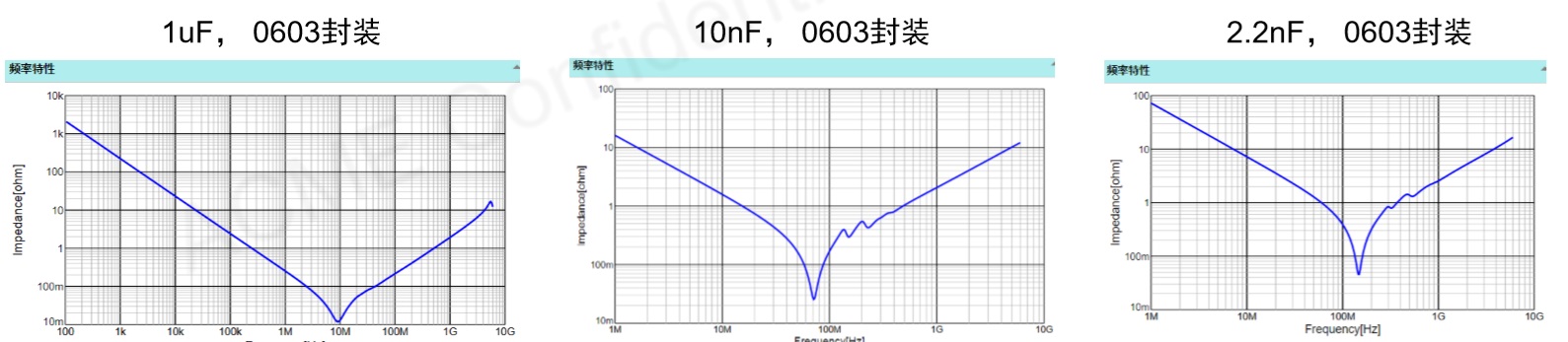

10nF, 0603封装2.2nF, 0603封装

PVDD管脚搭配去耦电容,电容尽量在和音频功放芯片在同一层PCB上,且尽量靠近功放芯片。

1uF,0603封装

合理搭配陶瓷电容的容值搭配,尽量让100kHz~0.6GHz之内低于1Ω

( Class D的噪声干扰基本影响范围在300MHz以内),高的开关频率(>768kHz )通常推荐1uF+10nF (根据实际情况调整),低的开关频率一般推荐4.7uF/10uF+100nF(根据实际情况调整)

1.1 PVDD去耦电容原理性分析

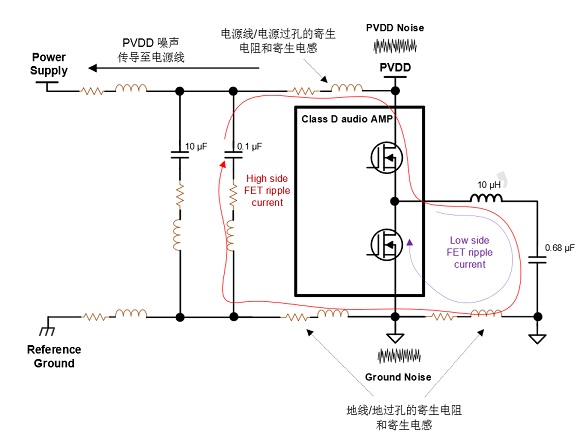

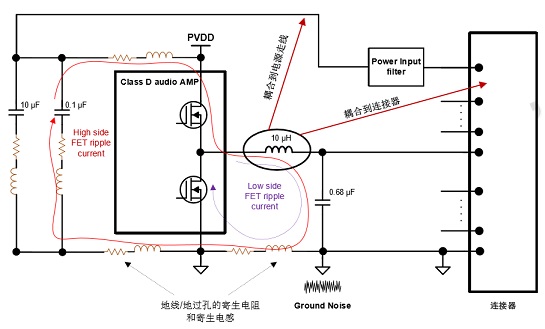

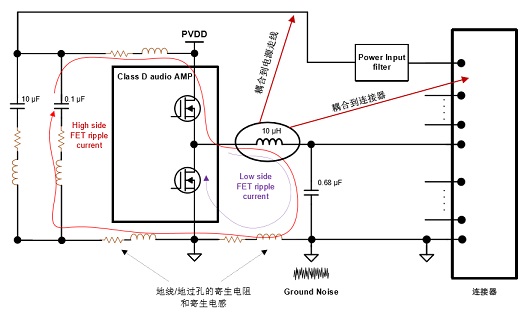

地噪声来源分析:由于开关纹波电流流过寄生电感/电阻,造成参考地(Reference Ground)和功放地之间的电压偏差。地噪声会通过音频功放传导至喇叭线(或者其他走线)影响传导/辐射测试结果。

电源噪声来源分析:开关纹波电流无法完全通过去耦电容压制在小环 路内部(红色环路内),导致 Power Supply上面有纹波电压。

Layout注意事项: 去耦电容尽量放在同一层,尽量靠近芯片, LC filter的输出电流回路尽量短,铜皮铺地尽量完整,各个电容的接地过孔充足,保证尽量小的回流路径阻抗。同层且靠近芯片的去耦电容放置比放在背面(Bottom层)的方案EMI在75MHz~100MHz之间要降低 ~12dB

2. 输出LC filter关键指标

1 应用在Class D Amplifier的电感最关键3个指标(和音频指标相关):

• 最大的输出电流(在不饱和的情况下)

• 感值vs电流曲线 (电流增大后的感值是否稳定)

• 直流电阻

2 应用在Class D Amplifier的EMI最关键几个因素:

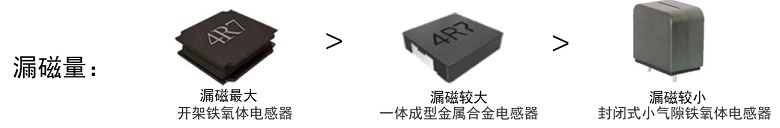

• 磁屏蔽性能。尽量选择磁屏蔽效果好的电感。 磁泄漏较差的电感容易对周围的电路造成干扰,尤其是喇叭线、电源输入走线或者附近的连接器。因为电感的磁泄露造成的EMI干扰频段主要集中在30MHz

• 电感尺寸。电感尺寸越小,与周边电路形成的寄生电容容值越小,因电场导致的干扰会越小。通常影响高频段部分(>30MHz)。

• 电感感值。尽量保证在工作电流范围之内的感值恒定,不要下降太多。

• 电容容值。电容容值随着工作电压的升高一般会呈下降趋势。偏置电压越高,电容容值下降越多,注意电容选型时留有足够的裕量。

2.1 输出LC filter的PCB设计注意事项

1 LC filter尽量靠近芯片,越近越好。

2 LC filter尽量远离PVDD 走线。由于电感的近场干扰影响比较大,会将开关噪声耦合到电 感周围的走线或者元器件。保持PVDD远离电感器可以改善传导测试结果。

3 LC filter尽量远离连接器。由于电感的近场干扰影响比较大,会将开关噪声耦合到连接器 或者线缆,造成EMI干扰。

4 良好的连接器屏蔽可以避免电感的近场干扰。

5 在LC filter的GND焊盘周围放置足量的接地过孔,保证足够低的噪声回流阻抗。

6 尽量在音频功放芯片所在的PCB层布置地平面或者地走线,这样可以避免过孔,从而获得最低的接地回流阻抗。

7 可以把扬声器的走线走在内层或者Bottom层,从而可以避免扬声器走线上的开关噪声耦 合到其他的走线(例如耦合到PVDD走线上)。

2.2 输出LC filter EMI噪声链路分析之一地噪声

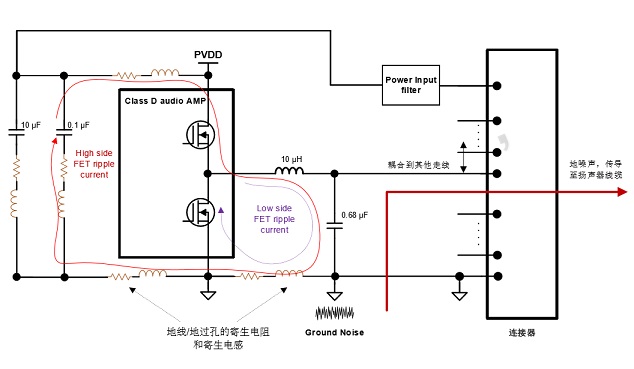

地噪声来源分析:由于开关纹波电 流流过寄生电感/电阻,造成参考地(Reference Ground)和功放地之间的电压偏差。地噪声会通过音频功放传导至喇叭线(或者其他 走线)影响传导/辐射测试结果。

Layout注意事项: 扬声器走线尽量内层屏蔽或者走背面避开其他走线。 LC filter 离音频功放器件越近越好。 LC filter的接地过孔尽量多。尽量和功放芯片同层铺地保证接地阻抗最小。

2.3 输出LC filter EMI 噪声链路分析之二-电场辐射dV/dT

功放Switching节点以及电感的电场噪声影响分析:电场噪声通常来自于功放的Switching Node和电感, 耦合到PVDD走线或者连接器的线 缆。通常影响的频段在30MHz以上。

Layout注意事项: LC filter 尽量靠近芯片来减少功放开关节点电磁辐射影响区域;尽量采用小尺寸的电感;让 LC filter远离PVDD走线以及连接器;对连接器进行屏蔽是最有效的方法。

2.4 输出LC filter EMI噪声链路分析之三-磁场辐射dI/dT

电感的磁场噪声影响分析:电感本省是一个比较强的磁场噪声源,耦合到PVDD走线或者连接器的线缆。 通常影响的频段在30MHz以内。

Layout注意事项: LC filter 设计过程中尽量选择漏磁比较小的电感 (通常一体成型金属合金电感比开架铁氧体电感在30MHz以内的频段能将EMI改善7dB以上);让 LC filter 远离PVDD走线以及连接器;

好的磁屏蔽电感相比差的磁屏蔽电感,对2MHz~30MHz 之间的影响差别达到7dB~17dB 。

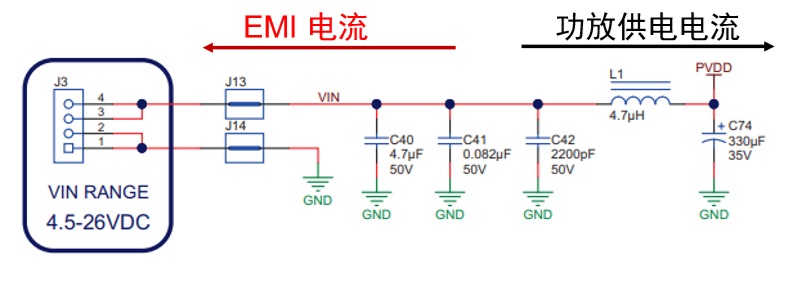

3 电源PI型滤波器

• L1, C40, C41,C42构成了一个电源线上的EMI滤波器

• 一般L1的感值选择0.68uH~4.7uH之间即可

• 电感的自谐振频率(SRF)越高越好(最好大于70MHz)。电感感值越小,自谐振频率一般越高。感值的大小和自谐振频率在系统设计中是一个权衡。

4 喇叭连接器设计注意事项

1 在每个连接器的pin附近放置一个~10nF的贴片陶瓷电容,离连接器越近越好。该方法一般在75MHz附近有~6dB的改善。

2 该电容具体的容值可根据实际的EMI测试结果进行调整。

3 放置足够多的地过孔,保证这些电容有良好的接地路径。

4 音频功放的开关节点附近以及电感产生很强的dV/dT 噪声,如果LC filter放置距离连接器 过近,电场能量会直接耦合到连接器或者喇叭线/电源线,从而直接影响到传导和辐射测试结果。对连接器进行有效的屏蔽(且屏蔽罩接地)会有比较好的效果,通常在100MHz~200MHz 改善~5dB。在LC filter本身离连接器比较近的情况下改善更明显,通常对FM频段和DAB频段(174MHz~239MHz)的改善会超过15dB。

5 散热器PCB接地屏蔽

一般散热器面积比较大,容易受到PCB板上的噪声耦合。散热器最好保证和功放有一个就近 接地点。所有耦合到散热器上的噪声能以最短路径流回音频功放,从而减小辐射。

某些情况下,散热器的接地与不接地甚至在100MHz~200MHz的频段范围会造成9dB的EMI 指标差异。

|